Google is using the RISC-V-based SiFive Intelligence X280 processor in combination with the Google TPU, as part of its portfolio of AI chips.

Fabless chip designer SiFive said that it was also being used by NASA, Tenstorrent, Renesas, Microchip, Kinara, and others.

RISC-V is an open standard instruction set architecture based on established RISC principles, which is provided under open source licenses that do not require fees.

At the AI Hardware Summit in Santa Clara, Krste Asanovic, SiFive's co-founder and chief architect took to the stage with Cliff Young, Google TPU Architect and MLPerf co-founder.

The SiFive Intelligence X280 is a multi-core capable RISC-V processor with vector extension, optimized for AI/ML applications in the data center.

At the summit, the two companies explained that the X280 processor is being used as the AI Compute Host to provide flexible programming combined with the Google MXU (systolic matrix multiplier) accelerator in the data center. However, they did not disclose the scale of the deployment.

SiFive has introduced the Vector Coprocessor Interface eXtension (VCIX), allowing customers to plug an accelerator directly into the vector register file of the X280.

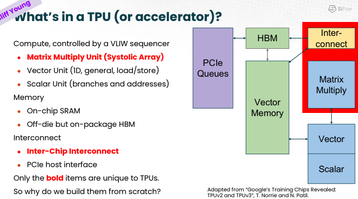

Google already uses third-party ASIC design services with Broadcom for its in-house TPU AI chip, instead focusing on developing its strengths - the Matrix Multiply Unit and the Inter-Chip Interconnect.

Now it is adding the X280 in what Google calls "an elegant division of labor with the TPU," taking the MXUs and combining them with the X280.

Google's Cliff Young said that with SiFive VCIX-based general purpose cores “hybridized” with Google MXUs, you can build a machine "that lets you have your cake and eat it too."