Al youtuber bitluni le gusta construir cosas raras. Visita su canal y podrás ver un video de él construyendo una pared de LED multicolor hecha con pelotas de ping pong y un escáner de sonar casero.

Recientemente, sus 250.000 seguidores también lo han visto crear su propio superordenador. Para ello, ha unido 16 “supercúmulos”, cada uno de ellos con 16 microcontroladores basados en RISC-V del fabricante chino WCH, para formar un “megacúmulo”.

El resultado es un ordenador de 256 núcleos capaz de alcanzar una frecuencia de reloj combinada de 14,7 GHz ("no es nada del otro mundo, pero tampoco está nada mal", según bitluni). A primera vista, no es precisamente una maravilla (Frontier, el superordenador más rápido del mundo, tiene más de ocho millones de núcleos de procesador), pero la máquina que bitluni ha montado en su taller demuestra lo que podría ser posible a mayor escala utilizando componentes basados en la arquitectura de chip de código abierto RISC-V.

La naturaleza abierta de RISC-V significa que los proveedores no deben pagar tarifas de licencias de propiedad intelectual (PI), por lo que los componentes pueden resultar baratos; los microcontroladores WCH cuestan menos de diez centavos cada uno, una cuarta parte del precio de dispositivos comparables basados en otras arquitecturas, lo que significa que bitluni pudo adquirir las piezas necesarias para su "megacluster" por menos de 30 dólares.

Pero más allá de proporcionar una opción de chip de bajo costo para proyectos domésticos, ¿puede RISC-V tener un impacto en los centros de datos? Los semiconductores basados en la arquitectura x86 de Intel siguen dominando, junto con un número cada vez mayor de dispositivos basados en Arm que están siendo desarrollados internamente por los hyperscalers de la nube. Pero algunos proveedores creen que sí y están lanzando productos que esperan que se conviertan en parte integral de los servidores del futuro, pero tienen mucho trabajo por delante para tener un impacto.

Gestión de RISC

RISC-V es un producto de la investigación realizada en el Laboratorio de Computación Paralela de la Universidad de California en Berkeley (California). Lanzado por primera vez en 2010, es una arquitectura de conjunto de instrucciones (ISA) modular, un grupo de reglas que rigen la forma en que un componente de hardware interactúa con el software. Como estándar abierto, RISC-V permite a los desarrolladores crear lo que deseen sobre la base de la ISA.

La organización sin ánimo de lucro RISC-V International administra la ISA y ha formado una comunidad de poco menos de 4000 miembros, entre los que se incluyen Google, Intel y Nvidia. En 2022, RISC-V International afirmó que había 10 mil millones de chips basados en su ISA en circulación en todo el mundo y predijo que esa cifra ascendería a 25 mil millones en 2027.

Muchos de estos chips son microcontroladores básicos que se incluyen en dispositivos Edge de bajo costo y sistemas integrados para productos como auriculares inalámbricos, en lugar de CPU avanzadas. Pero Mark Himelstein, director de tecnología de RISC-V International, dice que RISC-V está pensando a lo grande. "Todo lo que hacemos en RISC-V está impulsado por el centro de datos", dice.

El año pasado, la Fundación RISC-V presentó los perfiles; paquetes que contienen una ISA base acoplada con extensiones que funcionan bien juntas al construir un tipo específico de chip. “Podemos dárselos a los compiladores y a los encargados del sistema operativo”, dice Himelstein. “El primer perfil que salió se llama RVA, que está destinado a aplicaciones informáticas de propósito general como HPC y grandes cargas de trabajo de IA/ML. En realidad, no está dirigido a los usuarios de auriculares, aunque pueden usarlo”.

Himelstein afirma que esto es para ayudar a acelerar el desarrollo de chips RISC-V y refleja un creciente interés en los chips de servidor basados en ISA. “En el mundo posterior a ChatGPT, la gente se está volviendo mucho más agresiva con la forma en que integran la IA y el aprendizaje automático en cada aplicación y solución”, afirma. “Se necesita un buen hardware para poder hacerlo, y estamos viendo un número cada vez mayor de chips de servidor RISC-V que pueden impulsar la próxima generación de 'cajas de pizza'”.

Llegando al mercado

Ventana Micro Systems es una de las empresas que apuntan al mercado de servidores con hardware RISC-V. El año pasado, el proveedor anunció una segunda versión de su procesador Veryon, que cuenta con 192 núcleos integrados en un diseño de chiplet y está listo para la producción en el proceso de cuatro nanómetros de TSMC.

La empresa fue fundada en 2018 por ingenieros que anteriormente habían trabajado en el desarrollo de procesadores de 64 bits en la arquitectura Arm y vieron la oportunidad de hacer algo igualmente transformador con los semiconductores de alto rendimiento RISC-V.

"Si nos fijamos en el RISC-V actual, es básicamente un conjunto de microcontroladores", afirma Travis Lanier, director de productos de Ventana. "De hecho, creo que el RISC-V dominará por completo el mercado de los microcontroladores.

“Pero la gente lo verá y dirá: 'No es una ISA seria para un alto rendimiento'. Así que tenemos que demostrar que lo es haciendo avanzar RISC-V, y creo que ahora todas las características están ahí para competir con las otras ISA, se trata de ponerlas en una CPU”.

En términos de rendimiento, Ventana afirma que Veryon V2 puede superar a los procesadores para servidores Genoa y Bergamo Epyc de AMD, aunque dado que el V2 no se implementará hasta 2025, es probable que esta comparación sea algo anticuada. "Estamos terminando el diseño y esperamos que las primeras implementaciones en centros de datos se realicen a principios del próximo año", dice Lanier. "Serán implementaciones limitadas y buscaremos ampliarlas a partir de ahí".

Ventana planea aprovechar la flexibilidad de la arquitectura abierta de RISC-V para obtener una ventaja sobre sus rivales. Veryon V2 admite aceleración específica de dominio (DSA), lo que permite a los clientes agregar aceleradores personalizados. "DSA podría ayudar a los operadores de centros de datos a mejorar el rendimiento para cargas de trabajo específicas para satisfacer los requisitos de los clientes", afirma Lanier.

Muchos proveedores están pensando en líneas similares. SiFive fue uno de los primeros en proponer chips de alto rendimiento RISC-V y en 2022 se valoró en 2.500 millones de dólares tras una ronda de financiación de 175 millones de dólares. Al parecer, el hardware de la empresa se puede encontrar en los centros de datos de Google, donde sus chips ayudan a gestionar las cargas de trabajo de la IA, y la NASA le adjudicó un contrato de 50 millones de dólares para proporcionar CPU para el ordenador de alto rendimiento para vuelos espaciales de la agencia espacial estadounidense. Sin embargo, su progreso parece haberse estancado recientemente y, en noviembre pasado, se informó de que iba a despedir al 20 por ciento de su plantilla, incluida la mayor parte de su equipo de diseño de procesadores de alto rendimiento.

Otra startup, Tenstorrent, está construyendo su propia CPU RISC-V, así como un acelerador de IA que espera que pueda competir con las GPU de IA de Nvidia, que triunfan en todo. Está dirigida por Jim Keller, un ex arquitecto principal de Intel a quien se le atribuye un papel decisivo en el diseño de los procesadores A4 y A5 de Apple, así como del silicio personalizado para los coches autónomos de Tesla.

Los grandes nombres de la tecnología también se están sumando a la iniciativa. Samsung está creando un laboratorio de I+D en Silicon Valley dedicado al desarrollo de chips RISC-V, y Alibaba, que desde hace tiempo tiene interés en RISC-V, afirmó en marzo que estaba en camino de lanzar un nuevo chip avanzado para servidores basado en ISA en algún momento de este año.

Alibaba ya tiene en el mercado un chip de servidor RISC-V, el C910, que se puso a disposición en los servidores en la nube de la empresa francesa de centros de datos Scaleway en marzo. Scaleway afirmó que se trataba de la primera implementación de servidores RISC-V en la nube y añadió que espera que la arquitectura se convierta en dominante en el mercado a medida que los países "intente recuperar la soberanía sobre la producción de semiconductores".

Sébastien Luttringer, director de I+D de Scaleway, afirmó en su momento: «El lanzamiento de los servidores RISC-V es una declaración concreta y directa de Scaleway para impulsar un ecosistema en el que la soberanía tecnológica esté abierta a todos, desde el nivel más bajo hacia arriba. Esta iniciativa audaz y visionaria en un mercado emergente abre nuevas perspectivas para todos los actores».

Confía en el proceso

A medida que los chips comerciales RISC-V ganan impulso, la arquitectura también respalda los esfuerzos para desarrollar silicio de código abierto que podría llegar a los centros de datos.

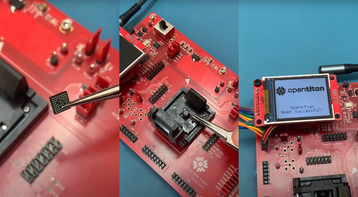

A principios de este año, la coalición OpenTitan alcanzó un hito cuando anunció lo que dijo que era el primer proyecto de silicio de código abierto en alcanzar disponibilidad comercial.

El chip, que cuenta con un núcleo de procesador RISC-V, es una raíz de confianza de silicio, un dispositivo de firmware que proporciona seguridad a nivel de hardware al detectar cambios realizados por ciberatacantes en una máquina y deshabilitar el hardware afectado.

OpenTitan fue fundado por Google en 2018 con el objetivo de desarrollar un chip de raíz de confianza de código abierto, y el proyecto se ha hecho realidad con la ayuda de lowRISC, una empresa de interés comunitario dedicada al desarrollo de silicio abierto, y una serie de otros socios de la industria y el mundo académico.

“El software de código abierto está presente en todos los proyectos”, afirma Gavin Ferris, director ejecutivo de lowRISC. “Es un éxito claro, pero el desafío para nosotros era cómo hacerlo con el hardware, porque compartir la propiedad intelectual básica tiene enormes ventajas.

“Tiene sentido económico compartir y amortizar el costo de los bloques de propiedad intelectual básicos para poder concentrarse en lo nuevo e innovador y reducir el tiempo de comercialización”.

LowRISC surgió del laboratorio de computación de la Universidad de Cambridge en 2014 y estaba buscando un primer caso de uso para impulsar hardware de código abierto cuando se topó con OpenTitan. Después de años de trabajo, un chip basado en IP desarrollado por el proyecto se fabricó a principios de este año y la coalición dice que es el primer semiconductor de código abierto que se ha construido con verificación de diseño de grado comercial y pruebas de alto nivel.

La propiedad intelectual ya está disponible para su uso y Ferris dice que confía en que los fabricantes de chips la adoptarán como parte de sus dispositivos. "Se trata de convertir en un producto básico, algo que no es la 'salsa secreta', y creo que hay un creciente reconocimiento de que la seguridad no es un área en la que la gente quiera diferenciarse", afirma. "Hay mucha ingeniería en cualquier SoC, y no tiene sentido hacerlo todo uno mismo; lo más inteligente es aprovechar el código abierto y concentrarse en las características del producto que se encuentran en un nivel superior de la pila y que se pueden vender.

“Eso no significa que no se puedan hacer cosas patentadas con [código abierto], solo significa que hay toda una capa de herramientas a las que se puede acceder y usar. Ya hemos visto esta película antes con el software y sabemos cómo termina, solo necesitamos llegar a una buena base para poner en marcha la máquina, porque una vez que comienza, no se detiene. Eso es lo que tenemos con OpenTitan”.

Desafíos futuros

Si bien el entusiasmo por RISC-V dentro de la comunidad de código abierto es alto, si esto es compartido en el mercado más amplio de centros de datos es otra cuestión.

Los chips para servidores han sido durante mucho tiempo el dominio de Intel y su arquitectura x86, aunque en los últimos años AMD, que diseña sus propias CPU x86, ha ido comiéndose ese dominio. El último informe de Mercury Research sobre el mercado de CPU, publicado en mayo, muestra que AMD tiene ahora una participación del 23 por ciento en el mercado de servidores gracias al éxito de su gama Epyc. Esto supone un aumento respecto del 18 por ciento de hace un año.

Intel y AMD también tienen que hacer frente al auge de los dispositivos Arm en los centros de datos. Los intentos anteriores de introducir la arquitectura de bajo consumo del diseñador de chips del Reino Unido en las salas de datos no han tenido éxito, pero las mejoras en su tecnología, combinadas con el deseo de los hyperscalers de la nube de desarrollar su propio hardware internamente, han impulsado un cambio de paradigma en los últimos tres años.

Amazon ofrece chips Graviton basados en Arm en sus centros de datos, mientras que Microsoft lanzó su CPU Cobalt 100 y el acelerador de inteligencia artificial Maia, ambos basados en Arm, antes de Navidad. Apple también tiene su propio silicio de consumo basado en Arm, tras haber abandonado a Intel en 2022, mientras que Nvidia tiene una CPU Arm, Grace, que se puede implementar junto con sus GPU o usarse como un producto independiente.

En otros lugares, proveedores como Ampere están construyendo chips dedicados para centros de datos basados en Arm que también están ganando terreno entre los hyperscalers.

Todo esto deja un espacio limitado para las CPU RISC-V en el centro de datos, afirma el analista de la industria de chips Dylan Patel de SemiAnalysis. “Arm está haciendo un gran trabajo a la hora de atraer a los grandes fabricantes, proporcionándoles mucho valor”, afirma.

“No solo proporcionan núcleos de CPU, sino también la red en chip que conecta la CPU a los controladores de memoria y los controladores PCIe. Incluso están haciendo cosas como colocar físicamente los transistores, por lo que están haciendo mucho para mantener y hacer crecer su mercado”.

Por este motivo, dice Patel, "no creo que RISC-V se convierta en la CPU central del centro de datos en un futuro próximo".

Patel también señala que los problemas de alto perfil en SiFive y los retrasos que ha experimentado Ventana para sacar un producto al mercado (la versión original del chip Veryon nunca llegó a producción) no han ayudado a la adopción. "Creo que el entusiasmo por RISC-V alcanzó su punto máximo en 2022", dice. "Desde entonces, SiFive ha despedido a su equipo central de CPU de alto rendimiento porque no estaban consiguiendo el impulso. Creo que afirmarán que siguen fabricando uno, pero a un ritmo mucho más lento.

“Ventana nunca sacó su primer chip y ha tenido algunos problemas. No están en crisis, pero definitivamente han sufrido una desaceleración y, si se juntan estos dos factores, se ve la dificultad de encontrar un caso comercial sólido para RISC-V”.

Él cree que los chips RISC-V pueden desempeñar un papel de apoyo en el centro de datos a través de dispositivos como el chip de raíz de confianza OpenTitan.

“Si estás fabricando un nuevo acelerador, necesitará tener instrucciones estándar”, afirma. “Eso está siendo estandarizado por RISC-V, y luego puedes salir y conectar todo lo demás tú mismo. Eso es algo que un puñado de personas están haciendo con aceleradores personalizados para centros de datos, ya sea que estén relacionados con el almacenamiento o con cargas de trabajo de IA”.

Meta es el ejemplo más interesante de esto, dice Patel. La empresa matriz de Facebook ha diseñado sus propios aceleradores de IA uniendo núcleos de CPU RISC-V construidos con IP de otro proveedor, Andes Technology, y tiene la intención de seguir utilizando la arquitectura en sus futuros esfuerzos en silicio. Patel dice que este es "probablemente el mayor aspecto positivo" para aquellos que esperan una mayor adopción de RISC-V en servidores.

En su intervención en la cumbre RISC-V celebrada en noviembre, Prahlad Venkatapuram, director sénior de ingeniería de Meta, afirmó: “Hemos identificado que RISC-V es el camino a seguir para todos los productos que tenemos en la hoja de ruta. Eso incluye no solo transcodificadores de vídeo de próxima generación, sino también aceleradores de inferencia y chips de entrenamiento de próxima generación”.

Si los ingenieros de Meta necesitan algún consejo sobre qué hacer a continuación, siempre pueden llamar a bitluni.

Este artículo apareció en el número 53 de la revista DCD. Léalo gratis hoy.