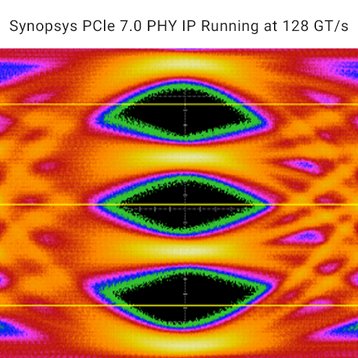

Synopsys has unveiled its new PCIe 7.0 IP solution, designed to reduce AI workload data bottlenecks within the data center.

The full stack solution consists of a controller, and IDE (Integrity and Data Encryption) security module, PHY (physical layer), and verification IP, offering 512GBps of bandwidth in a x16 configuration.

According to Synopsys, the new offering improves interconnect power efficiency by up to 50 percent and enables twice the interconnect bandwidth for the same chip perimeter compared to prior PCIe generations, while supporting all required features for backward compatibility.

The company said it will also reduce integration risk for AI and HPC networking chips by enabling fast and secure data transfers for every major interconnect in the AI/ML scale up fabric.

“It has been projected that in the next five years, the data center power specifically for AI clusters will increase by 80 percent and this solution helps address that challenge,” said Priyank Shukla, principal HPC IP product manager, Synopsys. “From the previous generation, this PCIe Gen Seven improves power efficiency by 50 percent, which will help the power for the AI clusters go down as the technology gets deployed.”

The solution will also be the first to use OpenLight Photonic IC technology to enable power saving over long-distance links. However, Shukla noted that the 50 percent efficiency figure relates to copper-to-copper transfers, with metrics for copper-to-optical transfers to be announced at a later date.

“Synopsis provides this interconnect technology to the whole ecosystem,” Shukla said. “This technology doesn't serve just one space, it provides the whole AI accelerator cluster with the silicon proven technology.”

“We are making the next generation of interconnect technology” he added.

The PCIe 7.0 IP offering will be rolled out in a phased manner to allow the ecosystem to be ready for the Gen Seven technology. The Synopsys Verification IP for PCIe 7.0 is available now, while the PCIe 7.0 Controller with IDE Security and PHY IP for advanced processes will be generally available in early 2025.